2.5D packaging and 3D IC packaging also differ in application scenarios and performance. 2.5D encapsulation is commonly used in high-performance computing, network communication, artificial intelligence, mobile devices, and other fields, with high performance and flexible design; 3D IC packaging is usually applied in fields such as memory, sensors, medical devices, etc., with high integration and small packaging volume.

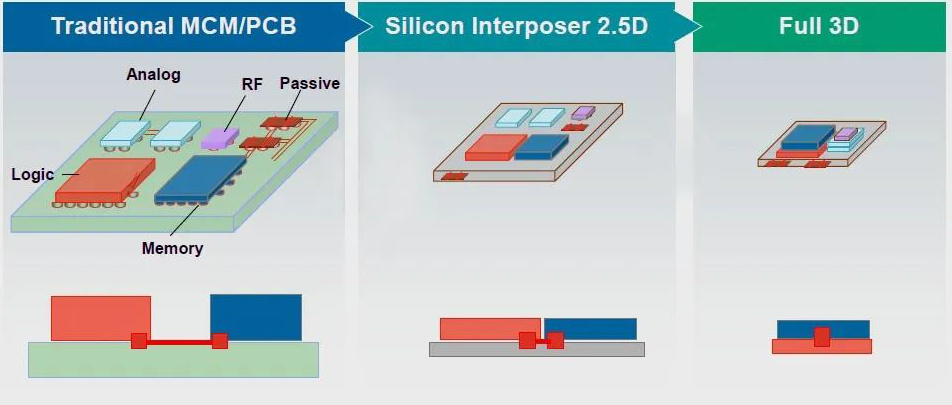

2.5D and 3D semiconductor packaging technologies are crucial for the performance of electronic devices. Both solutions have enhanced performance, reduced size, and improved energy efficiency to varying degrees. 2.5D packaging is beneficial for combining various components and reducing footprint. It is suitable for applications in high-performance computing and artificial intelligence accelerators. The principle of 3D packaging is to create transistor structures on chips and directly use silicon through holes to connect electronic signals from different chips, allowing for vertical stacking of memory or other chips on top. 3D packaging provides unparalleled integration, efficient heat dissipation, and shortened interconnect length, making it an ideal choice for high-performance applications. In the fast-paced semiconductor technology field, packaging plays a crucial role in determining the performance, size, and power efficiency of electronic devices. The two famous packaging technologies, 2.5D and 3D packaging, have become outstanding solutions. Each technology has unique advantages and challenges, which are factors that semiconductor manufacturers and designers must consider. We will explore the differences and applications between 2.5D and 3D packaging.

2.5D and 3D packaging

Understand 2.5D packaging

2.5D encapsulation, also known as 2.5D intermediate layer technology, is an intermediate step between traditional 2D encapsulation and mature 3D encapsulation. In a 2.5D package, multiple semiconductor chips using different process technologies are typically placed side by side on a silicon intermediate layer. The intermediary layer acts as a bridge, connecting various chips and providing high-speed communication interfaces. This arrangement allows for greater flexibility when combining different functions on a single package. The most popular 2.5D integration technology involves combining a silicon intermediate layer with TSV. In this configuration, the chip is typically connected to the intermediate layer using MicroBump technology. The silicon substrate used as an interpolator is connected to the substrate through bump connections. The surface of the silicon substrate is interconnected using redistribution layer (RDL) wiring, while TSVs serve as conduits for electrical connections between the upper and lower surfaces of the silicon substrate. The integration of silicon with TSV is the most common 2.5D integration technology. The chip is usually connected to the intermediate layer through Micro Bumps, and the silicon substrate as the intermediate layer is connected to the substrate through Bumps. The surface of the silicon substrate is wired with RDL, and TSV serves as the electrical connection channel between the upper and lower surfaces of the silicon substrate. This 2.5D integration is suitable for situations where the chip scale is relatively large and the pin density is high. The chip is generally installed on the silicon substrate in the form of Flip Chip. This 2.5D integrated form is very suitable for scenarios with large chip sizes and high pin density requirements. Usually, chips are mounted on a silicon substrate in a flip chip configuration.

Advantages of 2.5D packaging

Enhanced performance: The 2.5D package can integrate multiple components such as processors, memory, and sensors into a single package. This proximity leads to a shortened interconnect

length, thereby improving signal integrity and reducing latency. Size reduction: By stacking chips on the intermediate layer, 2.5D packaging reduces the overall footprint of the package

(compared to 2D), making it an ideal choice for smaller and thinner devices. Improve power efficiency: Shorter interconnects and optimized chip layout in a 2.5D package can reduce power

consumption, making it suitable for battery powered devices.

Application of 2.5D packaging

2.5D packaging has been applied in various industries, including high-performance computing, data centers, and network equipment. It is particularly suitable for artificial intelligence (AI)

accelerators, where multiple types of chips need to work efficiently together.

Understand 3D packaging

3D packaging takes integration to a new level by stacking multiple semiconductor chips together to create a three-dimensional structure. This method enhances the overall performance and functionality of the package. This will result in shorter interconnects and smaller packaging sizes. However, as chips delve into the true 3D-IC field (where logic or storage chips are stacked on top of each other), the design, manufacturing, and final yield and testing processes become more complex and challenging. The field of 3D packaging provides multiple methods to meet different requirements. There is a 'true 3D' packaging where wafers are intricately stacked together to achieve maximum integration. There is another type of "3D System on Chip (SoC) integration" that may involve functions such as stacking backside power distribution layers or memory wafers on top of each other. Finally, "3D System in Package (SiP)" involves a contact spacing of approximately 700 microns and utilizes fan out wafer level packaging. Each of these methods addresses specific technical requirements and challenges in the field of 3D packaging.

The advantages of 3D packaging

Unparalleled integration: 3D packaging allows for the most compact integration of various components and functions, enabling the creation of highly complex systems with a compact form factor.

Improving heat dissipation: The vertical arrangement of chips in 3D packaging can achieve efficient heat dissipation and solve the thermal challenges related to high-performance computing.

Shortening interconnect length: 3D packaging further shortens interconnect length (over 2.5D), thereby minimizing signal delay and power consumption to the greatest extent possible. A

significant advantage of 3D packaging technology is the reduction in distance. In a stacked 3D structure, the distance between each component is approximately 0.7 times the distance in a 2D

structure. The reduction of this distance directly affects the power consumption of the system wiring part, as it leads to a decrease in capacitance. Therefore, the current power consumption is

approximately 0.7 times that of 2D configurations.

3D Packaging Applications

3D packaging is mostly applied in the stacking of similar chips, where multiple identical chips are vertically stacked together and interconnected through TSVs that pass through the chip stack.

3D packaging is becoming increasingly popular in applications where extreme performance and miniaturization are crucial. It is typically used for advanced memory technologies such as high

bandwidth memory (HBM) and advanced processors for high-end smartphones, gaming consoles, and professional computing.