An IC wafer is a wafer made of an integrated circuit formed by many microelectronic components placed on a plastic base. It is a miniature electronic device. IC packaging refers to connecting the circuit pins on the IC chip to external connectors with wires for connection with other devices. The IC packaging form refers to the shell used to install the transistor IC chip. It not only plays the role of installing, fixing, sealing, protecting the chip and enhancing the electrothermal performance, but also connects the pins of the package shell with wires through the contacts on the chip, and these pins are in turn connected through the wires on the printed circuit board. Connect to other devices to connect internal chips to external circuits. Because the chip must be isolated from the outside world to prevent impurities in the air from corroding the chip circuit and causing a decrease in power efficiency.

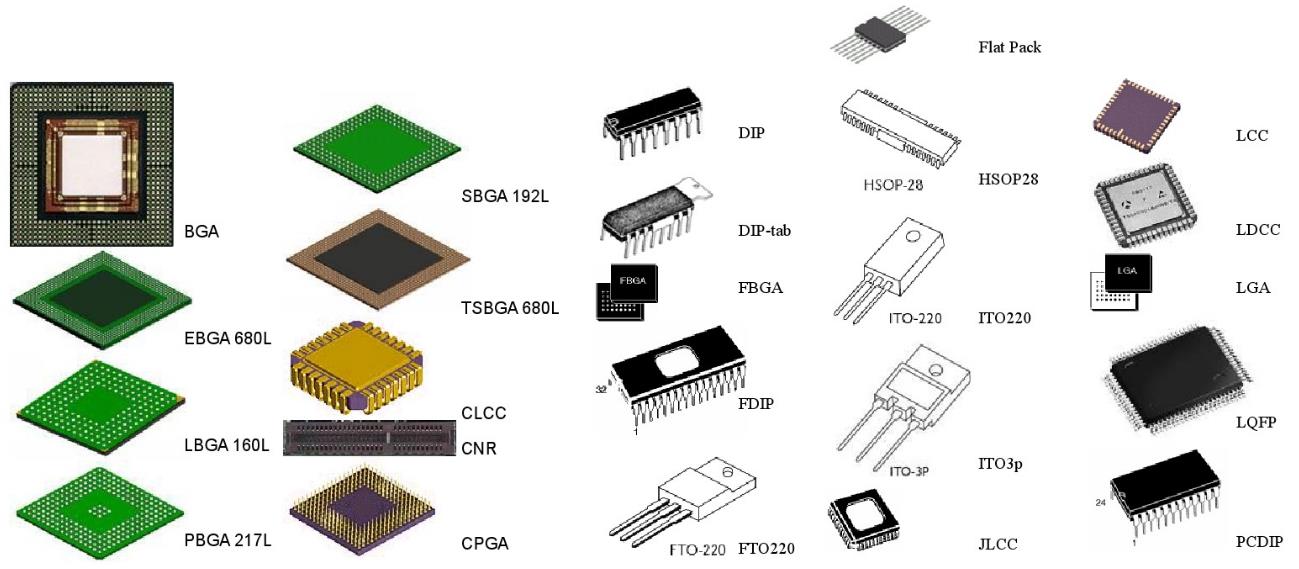

IC packaging form

IC packaging is basically divided into three categories according to materials: metal PCB, ceramic PCB, and plastic PTFE PCB. According to the form of electrode pins, it is divided into two types: through-hole plug-in type and surface mounting type. Each of these packaging forms has its own characteristics and different application fields.

1. Metal packaging

Metal packaging has good heat dissipation, good electromagnetic shielding, and high reliability, but it is not convenient to install and the cost is high. This packaging form is common in high-precision ICs or high-power devices.

2. Ceramic packaging

ICs encapsulated in ceramics have good thermal conductivity and high temperature resistance, but the cost is higher than plastic encapsulation, so they are generally high-end chips. Ceramic package ICs stipulated in national standards can be divided into flat type and dual in-line type, which are generally called DIP type abroad. However, flat package ceramic flat ICs have longer horizontal pins and are now replaced by SMT packages with shorter pins, which are rarely seen anymore. In-line ceramic package ICs have developed into the CPGA form as the number of pins increases.

3. Plastic packaging

This is the most common form of packaging. Its biggest features are simple process and low cost, so it is widely used. National standards stipulate that the forms of plastic packaging can be divided into two types: flat type (B type) and direct plug type (P type). With the addition of IC varieties and specifications and the improvement of integration, circuit packaging has become a highly professional field of process technology. Now, the names of IC packages at home and abroad are gradually becoming consistent. Whether they are made of ceramic materials or plastic materials, they are distinguished according to the pin layout of the IC.

In order to reduce costs and facilitate use, a large number of medium-power devices are now packaged in plastic. However, in order to limit the temperature rise and facilitate heat dissipation, the PV-DIP form of packaging is usually used, and a thermally conductive metal plate is also packaged to facilitate the installation of a heat sink.

4. IC pin arrangement

IC is a multi-pin device. When installing a chip on a circuit board, the pins must be inserted in strict accordance with their initial markings and arrangement order. The spacing between two adjacent pins of most ICs is 2.54mm (100mil), the wide spacing is 5.08mm (200mil), and the narrow spacing is 1.778mm (70mil). The distance between the two columns of pins of the DIP package chip is 7.62mm (300mil) or 15.24mm (600mil). There is usually a pin arrangement start mark on the surface of the IC. DIP packaged ICs usually have a circular concave spot or arc-shaped notch on the surface. When the start mark is located on the left side of the chip, the pin closest to this mark on the lower left side of the chip is defined as pin 1 of the IC, arranged in a counterclockwise direction.

IC package type

The general development process of packaging is probably TO → DIP → PLCC → QFP → PGA → BGA → CSP → MCM. The technology is advanced from generation to generation, and reliability has also been improved.

1. DIP dual in-line packaging. DIP refers to an integrated circuit chip packaged in a dual in-line form. Most small and medium-sized integrated circuits (ICs) use this packaging form, and the number of pins generally does not exceed 100. indivual. ICs in DIP packages have two rows of pins and need to be inserted into a chip socket with a DIP structure.

2. QFP/PFP type packaging. The distance between the chip pins of the QFP/PFP package is very small and the pins are very thin. Generally, large-scale or ultra-large integrated circuits use this packaging form. Chips packaged in this form must use SMD (Surface Mount Device Technology) to solder the chip to the motherboard.

3. BGA type packaging. With the development of integrated circuit technology, the packaging requirements for integrated circuits have become more stringent. This is because packaging technology is related to the functionality of the product. When the frequency of the IC exceeds 100MHZ, the traditional packaging pipeline may produce the so-called "CrossTalk" phenomenon, and when the number of pins of the IC is greater than 208 Pin, the traditional packaging pipeline has its difficulty. Therefore, in addition to using QFP packaging pipelines, most of today's high-pin-count chips have switched to using BGA (BALL Grid Array PACKAGE) packaging technology.

4. SO type packaging. SO type packaging includes: SOP (small outline package), TOSP (thin small outline package), SSOP (reduced SOP), VSOP (very small outline package), SOIC (small outline integrated circuit package) A package similar to the QFP form, but only a chip package with pins on both sides. This type of package is one of the surface mount packages, and the pins are led out from both sides of the package in an "L" shape.

5. QFN package type, QFN is a leadless quad flat package, a lead-free package with peripheral terminal pads and a die pad for mechanical and thermal integrity exposure. The IC packaging can be square or rectangular. There are electrode contacts on the four sides of the package. Since the lead-free mounting occupies a smaller area than QFP, it is also lower in height than QFP.