The most basic process of making a wafer is design->fabrication->packaging->testing. The cost of wafer is generally 20% of manpower cost, 40% of fabrication, 35% of packaging, and 5% of testing [for advanced process, the cost of fabrication may be more than 60%].

IC testing is in fact the cheapest step in all aspects of the wafer. In this fierce market where every company is shouting "Cost Down", labour costs are rising year by year, and both wafer fabs and packaging houses are on the second side of the market. In this fierce market where every company is shouting "Cost Down", labour cost is rising year by year, foundries and packaging houses are in the B-side market, and only IC testing is not so difficult to chew on, so the calculations of Cost Down fall on the head of IC testing.

But careful calculation, IC test save 50%, the total cost is only 2.5%, IC wafer or packaging to save 15%, IC test is equivalent to free. However, testing is the last hurdle for product quality. If there is no good IC testing and the product PPM is too high, the return or compensation is far beyond the 5% cost.

What kind of wafer testing is required in the wafer manufacturing process?

There are three main categories: chip function test, performance test, and reliability test, and one of the three major tests is indispensable for a chip product to be listed on the market.

IC testing

Function test is to see if the chip is right, performance test is to see if the chip is good, and reliability test is to see if the chip is firm.

1、IC function test is to test the parameters, name and function of the chip, in human words, it is to see whether the baby you gave birth to in October is a mule or a horse and pull it out for a walk.

2、IC performance test, due to the chip in the production process, there are countless possible steps to introduce defects, even if the same batch of wafers and packaging finished products, the chip has good and bad, so the need to carry out screening, as the saying goes, is to pick the stone in the egg, the "stone" chip to throw away.

3、IC reliability test, the chip has passed the function and performance test, got a good chip, but the chip will not be the most annoying static electricity in the winter bad, in thunderstorms, three volts, wind and snow days can work normally, and the chip can be used for a month, a year or ten years and so on, all these have to be evaluated through the reliability test.

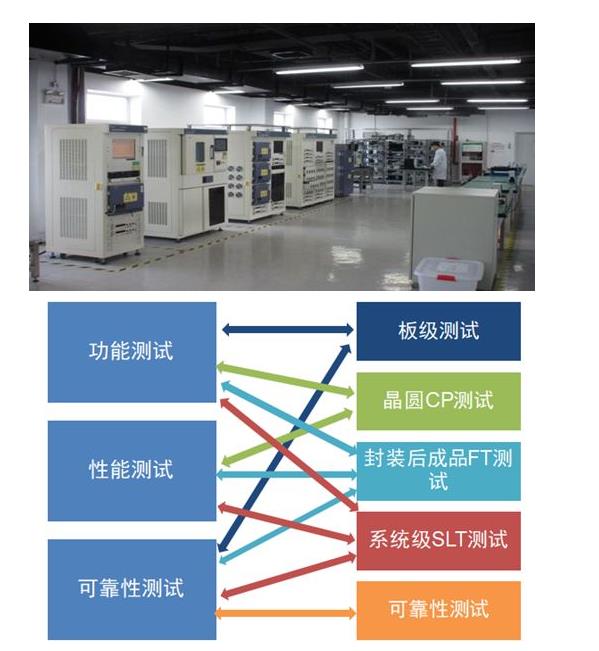

What means do we have to realise these IC tests?

IC test methods: board level test, wafer CP test, post-package FT test, system level SLT test, reliability test, and so on.

1、 IC board-level testing, mainly applied to functional testing, the use of circuit boards + chip to build an "analog" chip working environment, the chip's interface are led out to detect the chip's function, or in a variety of harsh environments to see if the chip can work properly. The equipment to be used is mainly instrumentation, and the EVB evaluation board is the main product.

2、 wafer CP test, often used in function and performance testing, to understand whether the chip function is normal, as well as filtering out faulty chips in the chip wafer. CP [Chip Probing] as the name suggests, is to use the probe to tie the wafer on the chip, to input all kinds of signals into the chip, to capture the output response of the chip and carry out comparisons and calculations, and there are some special scenarios that will be used to put down and adjust the chip [Trim]. The main equipment to be applied is the automatic test equipment [ATE] + probe station [Prober] + instrumentation, and the hardware to be made is the probe card [Probe Card].

3、 the finished product after packaging FT test, often applied to functional testing, performance testing and reliability testing, check whether the chip function is normal, and whether there are defects in the packaging process, and to help in the reliability test to detect after the "fire, snow and lightning" after the chip is not still able to work. Need to apply the equipment is mainly automatic test equipment [ATE] + robotic arm [Handler] + instrumentation, need to make the hardware is the test board [Loadboard] + test socket [Socket] and so on.

4、system-level SLT test, often applied to functional testing, performance testing and reliability testing, often as a finished product FT test supplement exists, as the name suggests, is a system environment for testing, that is, the chip into its normal working environment to run the function to detect its good or bad, the disadvantage is that it can only cover a portion of the functionality, the coverage is relatively low, so it is generally a complementary means of FT. The equipment to be applied is mainly a robot arm [Handler], and the hardware to be made is a system board [System Board] + test socket [Socket].

5、reliability testing, mainly for the chip to impose a variety of harsh environments, such as ESD static electricity, is analogous to the human body or analogous to the industrial body to the chip plus transient voltage. Another example is aging HTOL [High Temperature Operating Life], which is to accelerate the aging of the chip under high temperature and then estimate the life of the chip. There is also HAST [Highly Accelerated Stress Test] to test the moisture resistance of the wafer package, the product to be tested is placed under severe temperature, humidity and pressure test, whether the moisture will be along the gel or the interface between the gel and the lead frame to penetrate into the packaging body and thus damage the wafer.

IC testing

Wafer testing is definitely not a simple egg to pick the stone, not just "picky" "harsh" can, but also need to control the whole process and participation.

From the beginning of the chip design, we should consider how to test, whether to add DFT [Design for Test] design, whether through the design function of self-test [FuncBIST] to reduce the reliance on peripheral circuits and test equipment.

When the chip is opened for verification, the final test vectors should be considered, and the Test Bench for verification should be written in accordance with the cycle base pipeline, so that the generated vectors can be more easily converted and data leakage can be avoided.

At the Tapout stage, the chip test plan should be completed, and the ATE test programme development should be synchronised with the CP/FT hardware production to ensure that debugging is started as soon as the chip comes off the wafer production line, thus shortening the development cycle of the chip significantly.

Ultimately, it is even more important to enter the mass production stage, how to monitor and control the test yield, how to cope with customer complaints and low PPM, how to continuously optimise the test process, improve the efficiency of the test program, reduce the test time and test costs.

Therefore, IC wafer testing is not only a cost issue, but also a balancing art of quality + efficiency + cost!